Opened 17 years ago

Last modified 17 years ago

#33 new enhancement

Modèle FPGA SIMULINK — at Version 1

| Reported by: | jehanno | Owned by: | |

|---|---|---|---|

| Priority: | major | Milestone: | Finesse = 30000 |

| Component: | Digital Feedback System | Version: | 1.0 |

| Keywords: | Modele FPGA | Cc: |

Description (last modified by )

A l'occasion de l'intégration dans le modèle d'un second groupe de 4 SOS, des problèmes de peaks en sortie DAC ont été rencontrés. Il a été décidé de refondre la gestion des fréquences de travail des blocs dans le modèle du FPGA. Désormais, la fréquence principale est de 20MHz et seuls les blocs connectés à l'extérieur (ADC, DAC, I/O, SDRAM, Gain ADC, Gain DAC, Custom Regs) sont reclockés à 100MHz. Le schéma ci-dessous en illustre le principe :

Le 1er modèle correspondant est le 4.00 du 26.03.2009. Le résultat de la synthèse en occupation de ressources est le suivant :

MULT18X18s 58/168 > 34%

RAMB16s 29/168 > 17%

SLICEs 29997/46592 > 64%

TBUFs 96/23296 > 1%

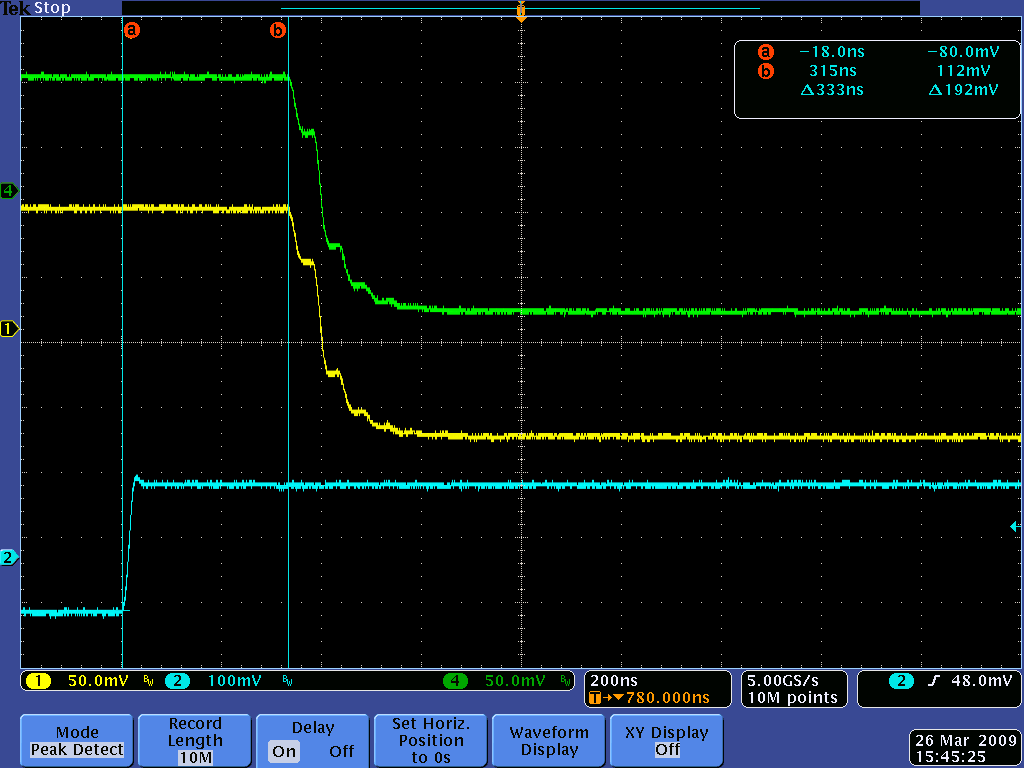

Avec des SOS cadencés à 20MHe au lieu de 10MHz avant, la calcul du à un coef prend donc 50ns. Des mesures de temps de latence ont été réalisées sur les SOS. Le plot ci-dessous correspond au cas SOSA1 et SOSB1 avec le 1er coef=65536, donc le minimum de latence in/out, soit 333ns relevés :

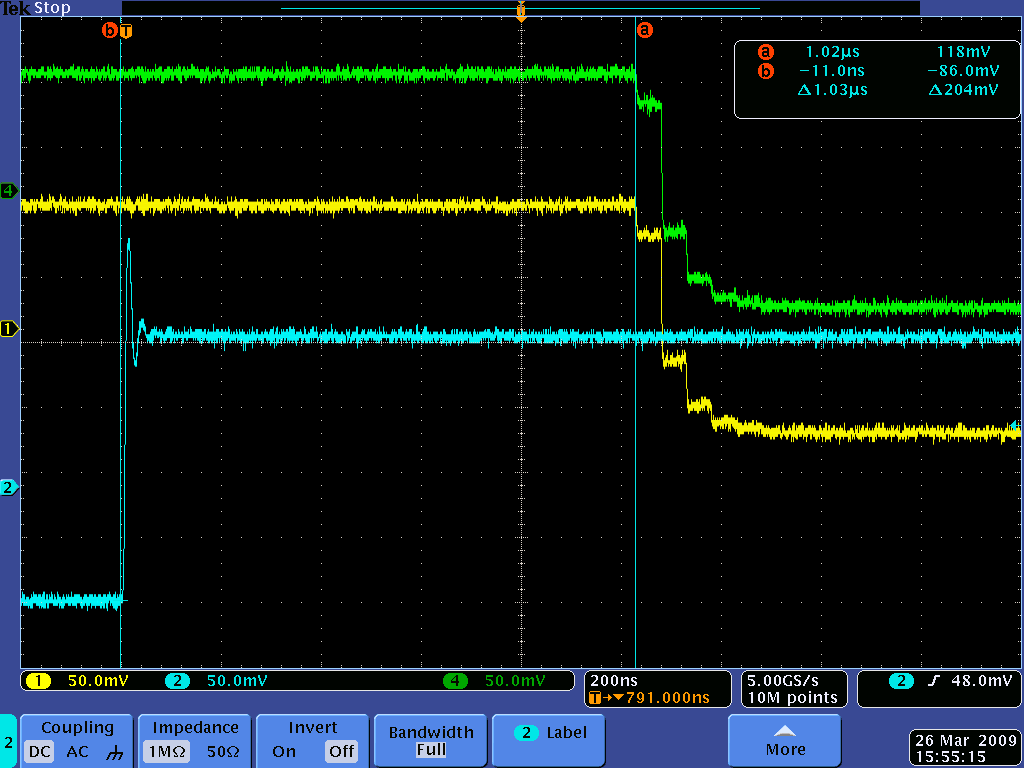

Le plot ci-dessous correspond au cas SOSA4 et SOSB4 avec le 3ème coef=65536, donc le maximum de latence in/out, soit 1.03µs relevés :

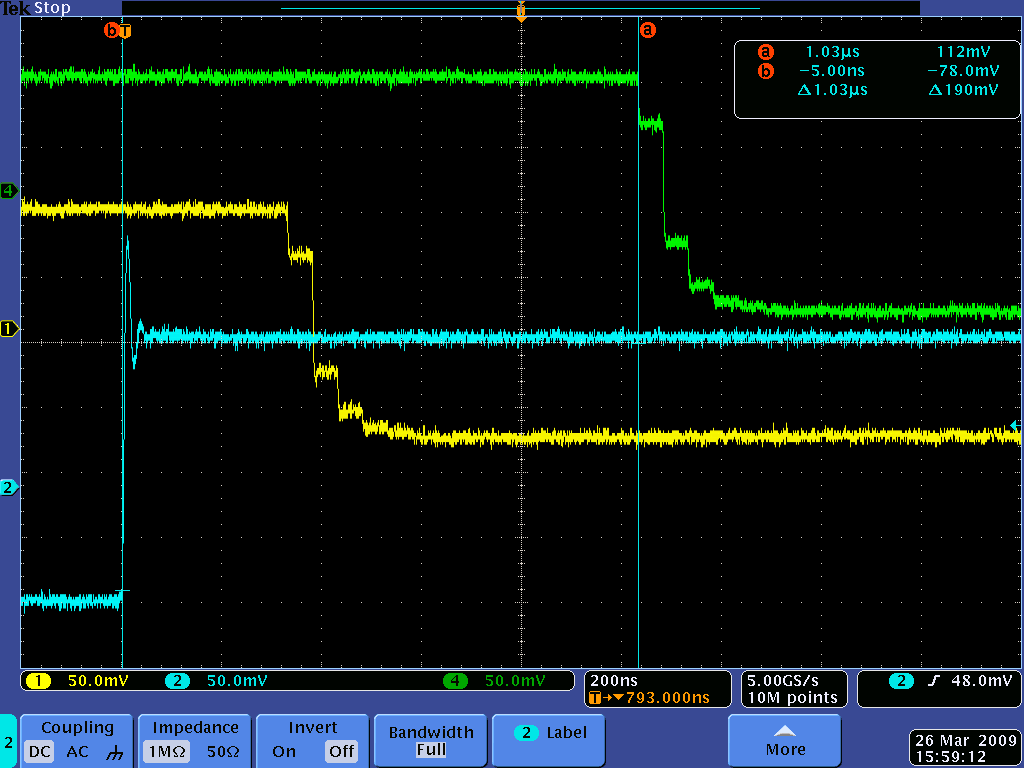

Le plot ci-dessous correspond au cas de minimum de latence pour SOSA et de maximum de latence pour SOSB :